研发一款面向ADAS应用的SoC芯片要花多少钱?

导航目录

1. 背景概述

我们今天的目标是评估一下,研发一款性能类似CV22的SoC(我们假定这个芯片的代号为VIO)的成本是多少:

- CPU:四核ARM Cortex-A53 1.0GHz

- DDRC:LPDDR4 Controller 32bit

- GPU:ARM Mali-400MP4

- NPU:2Tops

- Vin:3路MIPI 4lane,每路支持8M像素,支持虚拟通道

- 对应Vin的ISP、Encoder

- USB/Ethernet

- UART/SPI/SD/I2C若干

相信有了这些评估数据,我们就可以更加清晰的知道,要不要走向“芯片设计”的这条不归路,以及何时走这条“不归路”最划算。

本文在这里引用了大量最新的数据/资料甚至是价格,但这些数据均是从网上公开资料中获得,本文对此进行了归纳整理而已,若读者有心,这些信息都可以找到,甚至可以拿到更实时、更细致的原始数据。

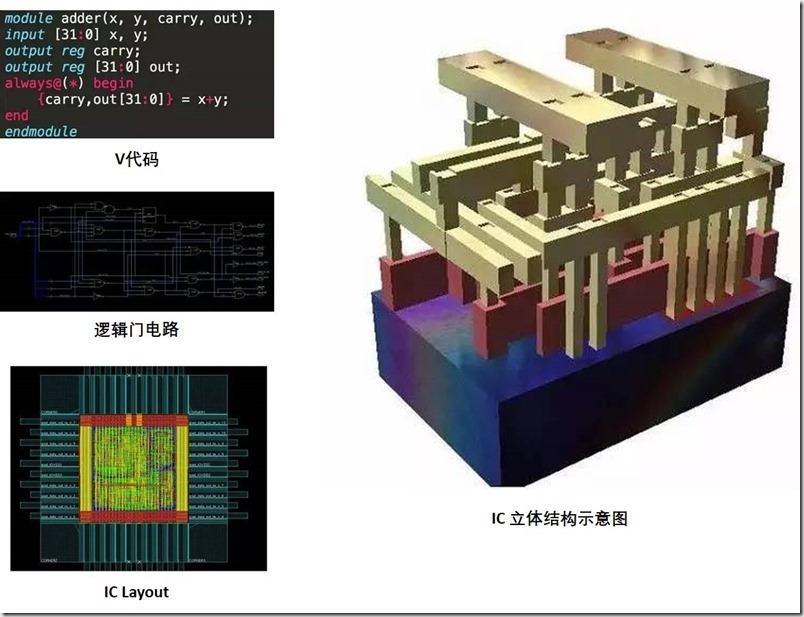

2. 芯片研发设计制造流程

在评估设计一款芯片需要花费多少钱之前,我们需要先大概了解一下IC设计及生产制造的流程有什么。

1. IC设计

- 前端设计:V代码 → 逻辑门电路

- 后端设计:Layout → “光绘文件”

- 版图验证:DRC、DFT、DFM

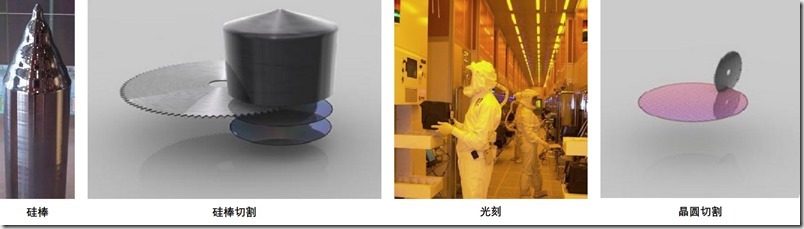

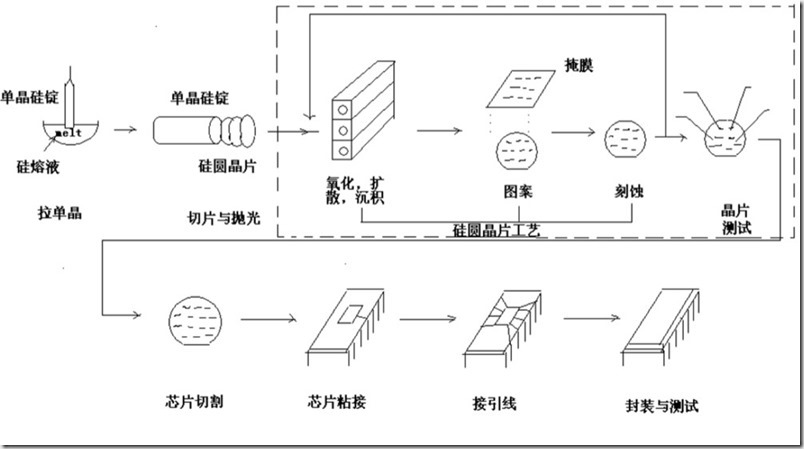

2. IC生产制造

- 单晶硅棒

- 切割、抛光

- 晶圆(Wafer)基板:镀膜、上光刻胶、光刻、离子注入

- 金属层:溅镀、上光刻胶、光刻、除胶

- 测试、切割、封测

- 发货

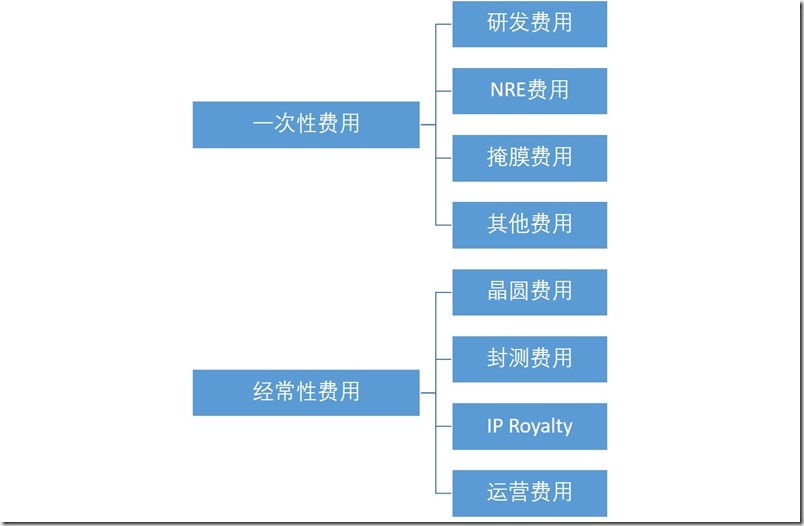

3. IC成本构成

IC的成本构成分为一次性费用与经常性费用两大部分。一次性费用是指的只要决定开芯片就要投入的钱,而跟后面芯片生产数量无关。经常性费用是指的芯片生产相关的费用,只要芯片在生产就要持续投入的钱,而如果芯片不再生产则不再需要付钱。

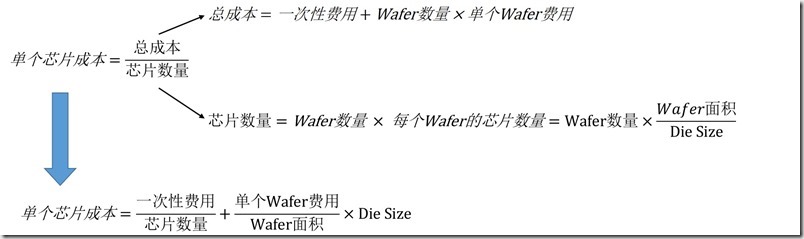

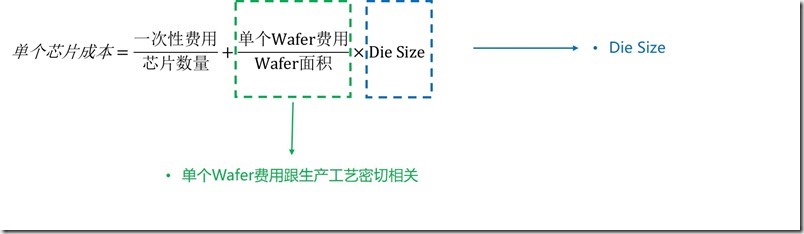

我们都知道,芯片行业是一个高投入、高风险、高回报的行业。其中重要的原因就是高昂的一次性费用。当决定开芯片时,公司需要支付高昂的费用,但芯片设计出来之后,其巨大的用量又可以摊薄前期的巨大投入。下面公式就展示出来了芯片成本的秘密:

下面公式的左边部分,一次性费用/芯片数量,主要由芯片设计公司决定,这是第四章要讲的内容。而右边部分则主要由工艺、Fab厂决定,这是第五章要讲的内容。

4. 一次性费用

一次性费用主要包含:研发费用、NRE费用、掩模费用以及其他费用。

4.1 研发费用

研发费用其实并不好评估,因为研发一款芯片的过程中,谁也不知道别家用了多少人,动用了多少研发资源。但好在我们只需要大概评估一个期望值,也即平均值。我们通过翻看国内各大IC上市公司的财务报表发现一个规律,在IC研发费用中,不管哪种类型的IC公司,研发人员的薪酬平均占比都在50%左右(i.e. 晶丰明源 47.6%,晶晨股份62.7% )。

|

半导体公司 |

主营业务 |

研发人员数量 |

研发人员比例 |

研发薪酬合计/万元 |

研发投入比例 |

硕士比例 |

本科比例 |

公司营业额/万元 |

备注 |

|

晶丰明源 |

照明IC |

149 |

58.89% |

1819 |

9.94% |

21.5% |

57.7% |

38440 |

半年报 |

|

晶晨股份 |

机顶盒SoC |

712 |

79.11% |

16350 |

27.6% |

40.5% |

51.3% |

94505 |

半年报 |

|

瑞芯微 |

消费类SoC |

553 |

76.1% |

– |

22.0% |

31.6% |

57.5% |

140772 |

|

|

兆易创新 |

存储及MCU |

586 |

68.6% |

– |

11.8% |

48.1% |

42.7% |

320292 |

|

|

汇顶科技 |

触屏IC、指纹IC |

1700 |

91% |

– |

27.3% |

50% |

– |

305609 |

半年报 |

通过仔细查看报表,我们发现目前国内IC公司研发人员的平均薪酬为每人¥30w/年。

至此,我们就有了一个基本的概念:

- 总研发投入可以由研发人员总薪酬 × 2估算。

- 研发人员总薪酬在当前 = 30w × 研发团队人数。

- 因此,总研发投入 = 60w × 研发团队人数。

而根据行业内的经验,按照一年出一款IC(但可能对应多个型号)计算:

- 小型IC(电源/逻辑)研发团队最少可以低于10人:模拟、数字、Layout、测试、AE、项目管理,单项目研发投入在¥500w级别

- 大型IC(SoC)研发团队至少需要百人规模:每个模块可能就是一个小团队,单项目研发投入在¥5000w级别

4.2 NRE费用

SoC中的很多模块研发需要海量的人力/资金投入,尤其是MIPI/DDRC/USB/Ethernet等高速模块。而避免将人力耗费在这种基础通用模块上的最佳方法便是采购商业化的IP核。采购IP核可以显著降低研发人数与研发投入,但同时也带来了不菲的IP NRE费用。

IP授权费根据费用收取方式分为两种:

- NRE费用:一次性收取,每笔$几十万-千万

- IP Royalty:每pcs出货都会收取,$美分-$美金

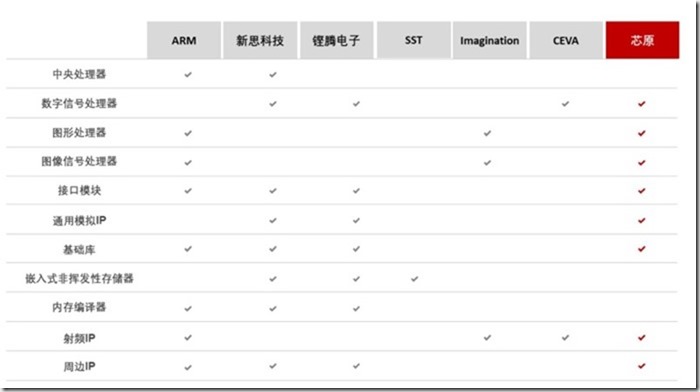

有的IP核两笔费用都会收取。像国内国际知名的IP核提供商有这些:

我们在这里列一些市面上收集到的公开的NRE费用,都是大概的价格。IP供应商肯定不会明码标价:

- ARM Cortex-A53: $200k-300k

- ARM Cortex-A55: $1.5M

- ARM Mali-G53: $500k

- ARM Mali-400: $200k-300k

当然了如果IP核使用量很大,还可以跟IP核供应商谈更多的玩法。比如可以跟IP核供应商谈一个限期买断的条款。买断之后,在该时间段内可以无限次使用该IP核,但价格可能是单次NRE费用的数倍。

4.3 掩模费用

IC设计完了之后要流片做芯片的验证,而掩膜费用又占流片费用的大头。

掩模费用由很多因素决定,通常包含了芯片所采用的工艺以及Metal层数。

我们在这里收集了一下网上公开的掩膜费用的价格:

- 40nm,40层:$1.5M

- 28nm SOI,层数未知,$4M

- 28nm HKMG,层数未知,$6M

- 16nm,层数未知:$5M

- 7nm,10层:$20M

看起来都挺吓人的。但其实这都是一种芯片独占一片晶圆的方式,我们称这种方式为Full Mask,中文名为:全掩膜。如果公司比较小,流片方式可以更加灵活,可以采用跟别的厂家拼板共用一片晶圆的方式。我们称这种方式为MPW,中文名为:多项目晶圆。MPW项目一般由一些政府机构牵头组织,每个项目的流片费用大概控制在$10k级,可以大大节省IC设计公司前期原型验证时的开销。

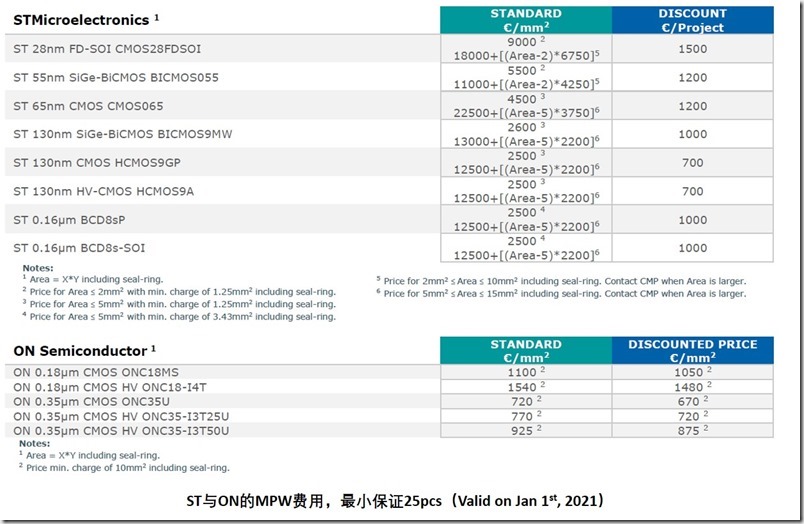

下面是ST与ON的MPW费用,最小保证25pcs。价格是2021年1月1日最新更新的:

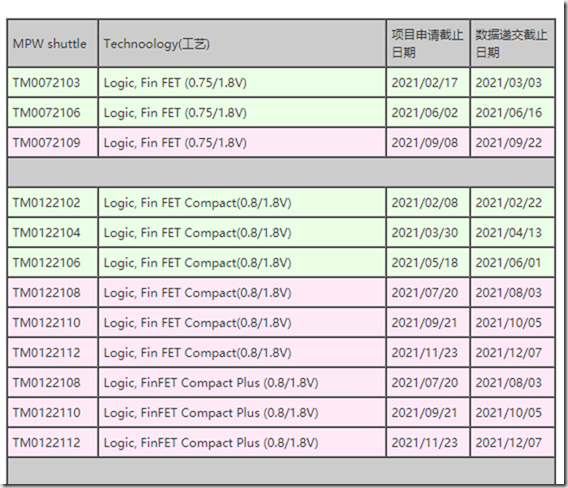

中国也有类似的项目,比如由“上海集成电路技术与产业促进中心”主办的MPW项目,虽然费用没有明码标价公布在网站上,具体费用我们不得而知。但它在官网上公布了流片的时间表,供各IC设计公司参考。

4.4 其他费用

其他费用主要包含:

- 管理费用

- 场地费用

- EDA工具费用

- 服务器费用

- FPGA开发板费用

- 测试仪器费用

4.5 举例与总结

我们以一个小型电源类IC以及一个SoC为例,估算了一次性开支的各个环节的费用:

看起来,对于一个公司而言,不管是开一个小型IC还是大型的SoC,都要投入千万元人民币级别的一次性费用。

有没有降低一次性费用的方法呢?有。降低一次性开支的法宝,就是——外包。外包的本质是将一次性开支转嫁到经常性费用的“软性毒品”,但它是否是毒品,还要看外包的那一部分是“不能做的”or“不必做的”。如果自己技术都掌握了,仅仅是为了节省开支选择外包,那就外包公司而言不形成强依赖,那就不算是“毒品”。但如果外包公司掌握了自己没有掌握的核心科技,对外包公司形成了强依赖,那说它是“软性毒品”也不为过。

话说回来,IP外包也是外包的一种,它节省了IP开发费用,但可能会带来后续持续的IP Royalty支出。

如果我们选择将IC设计全部外包,走Turn-key方案,那么一次性开支可以低至上述成本的1/5-1/3。但与此同时我们也要知道,选择外包之后,后续的“经常性费用”就会升高。

5. 经常性费用

经常性费用主要是指的公式的右半部分。

市面上的Wafer主要以8英寸/12英寸为主。单个Wafer的费用主要跟Fab厂的生产工艺相关,每个Fab厂都有报价,我们可以想办法获取到。所以我们可以看护,经常性费用的大小,主要由Die Size决定。Die Size大,芯片的成本就高。Die Size小,芯片的成本就低。在芯片出货量大到一次性费用可以忽略的时候,Die Size就成了决定芯片成本的最重要的因素。

5.1 Wafer费用跟工艺的关系

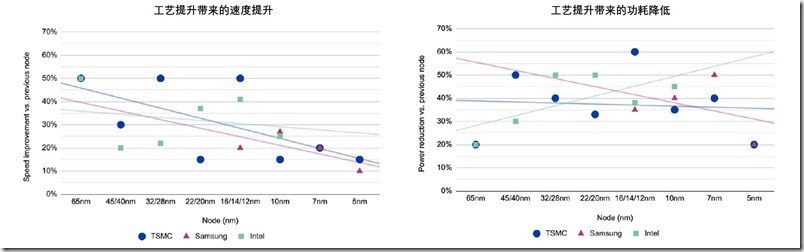

我们都知道,工艺越先进,性能越高:

但与此同时,选择越先进的工艺,付出的代价也就越大。代价之一就是可选的供应商会越来越少。

|

工艺(nm) |

180 |

130 |

90 |

65 |

45/40 |

32/28 |

22/20 |

16/14 |

10 |

7 |

5 |

|

量产时间 |

1999 |

2001 |

2004 |

2006 |

2009 |

2011 |

2014 |

2015 |

2017 |

2018 |

2020 |

|

Fab厂数量 |

94 |

72 |

48 |

36 |

26 |

20 |

16 |

11 |

5 |

3 |

3 |

|

光刻机供应商 |

4 |

3 |

2 |

2 |

2 |

2 |

2 |

2 |

2 |

2 |

1 |

在180nm的年代,我们可以选择的Fab厂在全球范围内有94家。而180nm工艺的光刻机供应商全球也有4家。但到了5nm,全球范围内只有3家Fab厂可以做,而且光刻机供应商只有1家(ASML)。

选择更先进的工艺的另外一个代价是单位Wafer的成本急剧升高。下表是TSMC的12寸晶圆的单片报价,我们可以看到从7nm开始,TSMC的晶圆报价急剧上升,单片Wafer价格到了16988美金。

|

工艺(nm) |

90 |

65 |

40 |

28 |

20 |

16/12 |

10 |

7 |

5 |

|

晶体管密度 MTr/mm2 |

1.6 |

3.3 |

7.7 |

15.3 |

22.1 |

28.9 |

52.5 |

96.3 |

171.3 |

|

每片Wafer售价 |

$1,650 |

$1,937 |

$2,274 |

$2,891 |

$3,677 |

$3,984 |

$5,992 |

$9,346 |

$16,988 |

|

每mm2 Wafer单价 |

$0.028 |

$0.032 |

$0.038 |

$0.048 |

$0.061 |

$0.066 |

$0.100 |

$0.156 |

$0.283 |

|

VIO的Die Size (mm2) |

938 |

455 |

195 |

98 |

68 |

52 |

29 |

16 |

9 |

|

每个Wafer芯片数量 |

62 |

129 |

303 |

606 |

874 |

1145 |

2057 |

3733 |

6644 |

|

每个Die成本 |

$26.70 |

$15.05 |

$7.51 |

$4.77 |

$4.21 |

$3.48 |

$2.91 |

$2.50 |

$2.56 |

我们假设VIO芯片内部有15亿颗晶体管,那么根据不同工艺的晶体管密度,我们可以计算出VIO的理论最小Die Size。根据TSMC的报价,对于VIO这种规模的集成电路而言,单就经常性费用,并不是5nm工艺最划算。上表可以看出,选择7nm工艺会比选择5那么工艺更划算。再考虑到一次性费用的支出,很可能选择10nm或者12nm是更划算的选择。而事实上,CV22也没有使用7nm工艺。

总结下来就是:

- 工艺越先进,一次性开支越高

- 工艺越先进,每Wafer售价也越高

- 工艺越先进,单位面积的芯片数量越多,平摊下来价格越低

结论:最先进的工艺不一定最贵,最成熟的工艺不一定最便宜

5.2 IP Royalty

常见IP Royalty价格:

- ARM Cortex-A53 $0.2-0.3/pcs

- ARM Mali-400MP4 $0.3/pcs

- H.264/H.265 Encoder $0.5/pcs

- RISC-V 0

以上价格仅用于让大家对价格的数量级有直观感知。RISC-V之所以是0是因为它是开源内核,无需授权费用。但市面上还有一些商业化的RISC-V内核,使用商业内核会得到一些技术支持,这种商业内核的费用就不见得是0。

5.3 Die Size

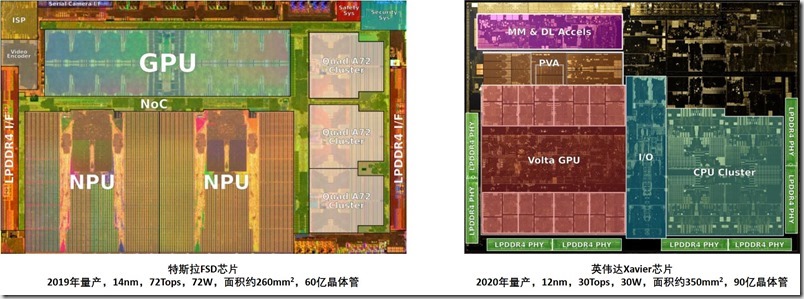

两个大型车载运算芯片Die Size分析:

从这个图里我们可以很清晰的看到不同的模块占用的Die Size的大小。对于我们这种要研发的芯片来说,Die Size更多的要靠经验。下表中的数据是笔者根据经验估算出来的16nm工艺下的Die Size,不是测量值,没有太强的参考意义。

|

模块 |

Die Size(mm2) |

VIO内部对应模块数量 |

VIO对应模块Size(mm2) |

|

4核Cortex-A53 |

4.5 |

1 |

4.5 |

|

4核Cortex-A9 |

6.2 |

||

|

双核A15 |

6.8 |

||

|

ISP 360MP/s |

6.3 |

1 |

6.3 |

|

MIPI-CSI2 4lane |

1.5 |

2 |

3 |

|

LPDDR4 Controller 32bit |

4 |

1 |

4 |

|

USB/SPI/I2C/UART |

4 |

1 |

4 |

|

NPU 4Tops |

6 |

1 |

6 |

|

电源+内部总线 |

– |

1 |

14 |

|

总计 |

41.8 |

表格中故意把Cortex-A9以及Cortex-A15内核的Die Size写在这里,好让大家对各种ARM内核的大小有一个直观的认识。

5.4 封测+其他费用

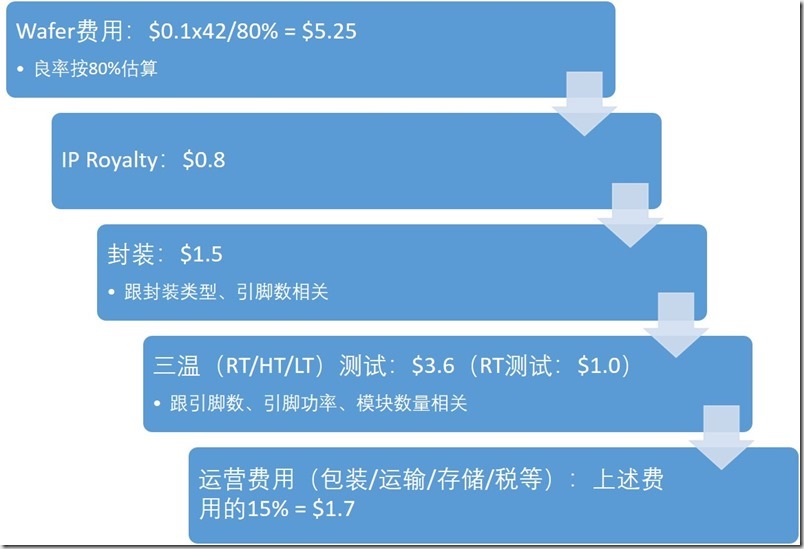

我们在这里还是以VIO芯片为例:

我们可以估算总成本约$12.8元。

其中:

- Wafer成本占40%

- 封测费用:

- 工规$2.5,占比19%

- 车规$5.1,占比40%

由此我们可以看出,车规比工规,总费用要高出25%左右。这里面的差别最主要还是封测费用。

6. 费用总结

我们来总结一下开VIO这颗芯片的费用:

费用 = $30M + N×$12.8

其中$30M表示一次性费用是3000万美金,$12.8表示后续每生产一片芯片要额外投入12.8美金的成本。

如何降低成本

成本还是可以想办法降低的,我们能想到的有:

- 研发全部外包。

这样不必再养一只IC Design的团队,NRE费用也可以跟其他项目均摊。研发费用可以减少$7M,NRE费用可以减少$12M,其他费用可以减少$1M。但后续运营费用会增加10%。因此费用公式变成了:

费用 = $10M + N×$14 - 在研发全部外包的基础上,更换16nm工艺为22nm工艺。

研发费用可以降低$2M,但会使得Die Size增大90%,单片Wafer价格节省42%。

费用 = $8M + N×$15 - 在研发全部外包的基础上,更换16nm工艺为12nm工艺

16nm换成12nm可没有那么神奇,让Die Size减少很多。更换工艺之后Die Size只能减少5%左右。因此:

费用 = $10M + N×$13.8 - 在研发全部外包的基础上,去掉那些实用性没有那么强的模块,砍掉1路MIPI并将MIPI接入能力降低为4MP/s,去掉GPU

根据5.3中的表格,我们可以估算出来Die Size可以减少30%左右。在这样的情况下,

费用 = $10M + N×$10

如果再进一步更换为22nm工艺:

费用 = $8M + N×$10.6

数据已经罗列的足够清楚了,虽然这些数据不一定可信,大部分基于网络上的公开数据,少部分是基于个人经验的推测,但对于定性的了解一颗ADAS主控芯片的成本还是会有很大帮助。至于开发周期、车轨认证等问题,这些本来应该是小问题,但在今年也变成了大问题。最近IC的交付很困难,车载的IC尤其难,各家的周期、交付都很不一样,门道很多,这里就不再一一道来了。

长知识了!

厉害!!!